새로운 소식: 인텔은 무어의 법칙을 끊임없이 추구하면서 향후 10년 동안 컴퓨팅을 발전시키고 가속화하는 데 필수적인 핵심 패키징, 트랜지스터 및 양자 물리학 혁신을 공개하고 있습니다. 에서는 IEEE 인터내셔널 일렉트론 디바이스 미팅 (IEDM) 2,021 인텔 하이브리드 본딩 장비에서보다 10 배 배선 고밀도화를 향한 경로를 설명 트랜지스터 스케일링, 새로운 전력 및 메모리 기술의 주요 혁신 및 새로운 30 % 내지 50 % 면적 개선 언젠가는 컴퓨팅에 혁명을 일으킬 물리학의 개념.

“Intel에서는 무어의 법칙을 발전시키는 데 필요한 연구와 혁신을 멈추지 않습니다. 당사의 구성 요소 연구 그룹은 IEDM 2021에서 업계와 사회가 의존하는 강력한 컴퓨팅에 대한 끝없는 요구를 충족하기 위해 혁신적인 프로세스 및 패키징 기술을 제공하는 주요 연구 혁신을 공유하고 있습니다. 이것은 우리 최고의 과학자와 엔지니어들의 지칠 줄 모르는 노력의 결과입니다. 그들은 계속해서 무어의 법칙을 지속하기 위한 혁신의 최전선에 서 있습니다.”

– Robert Chau, Intel 선임 연구원이자 구성 요소 연구 본부장

중요한 이유: 무어의 법칙은 메인프레임에서 휴대폰에 이르기까지 모든 기술 세대의 요구 사항을 충족하는 컴퓨팅 혁신을 추적해 왔습니다. 이러한 진화는 무제한 데이터와 인공 지능이 있는 컴퓨팅의 새로운 시대로 이동함에 따라 오늘날에도 계속되고 있습니다.

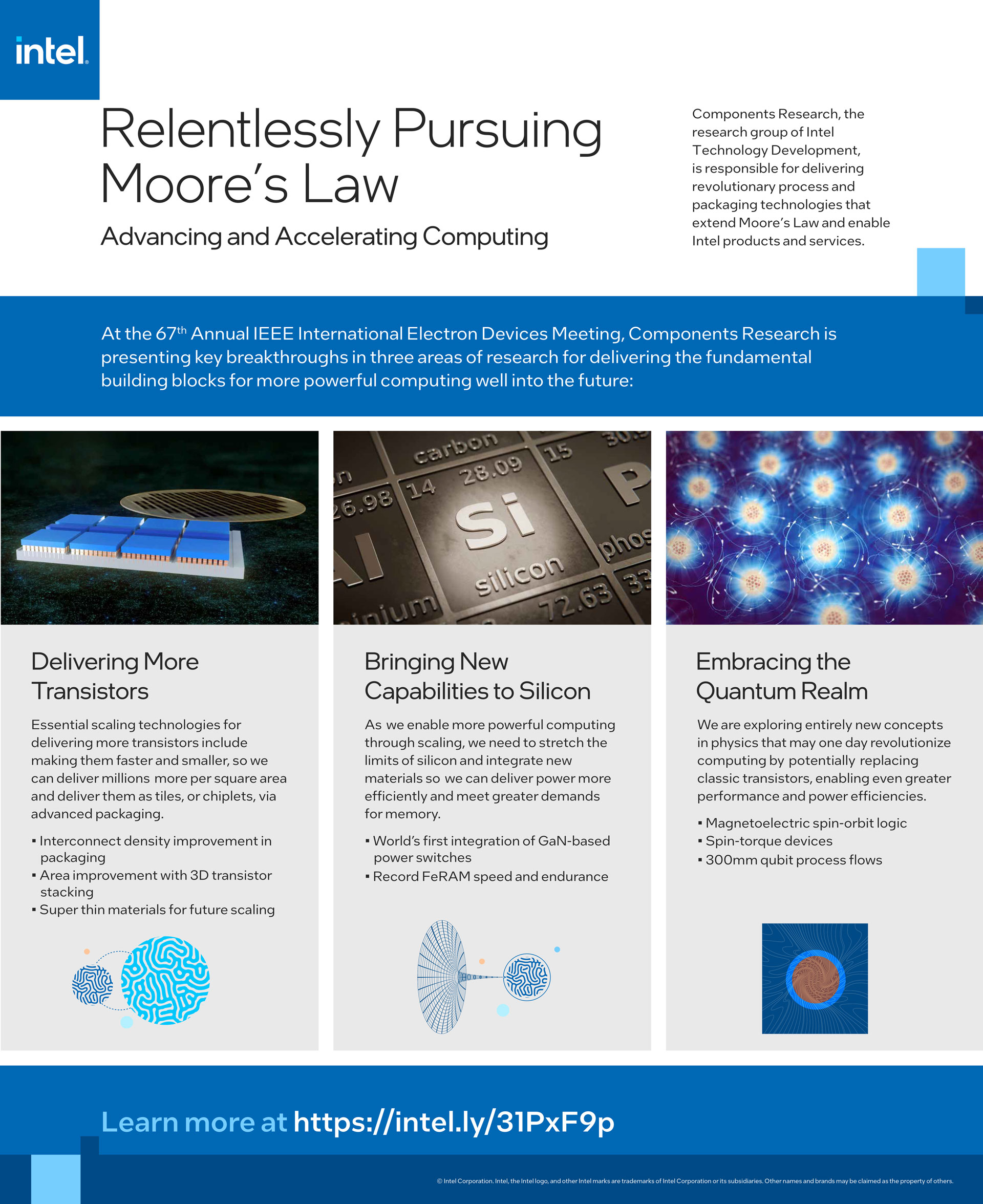

지속적인 혁신은 무어의 법칙의 초석입니다. 인텔의 구성 요소 연구 그룹은 세 가지 주요 영역에서 혁신을 위해 최선을 다하고 있습니다. 더 많은 트랜지스터를 제공하기 위한 필수 확장 기술; 전력 및 메모리 이득을 위한 새로운 실리콘 기능; 그리고 물리학의 새로운 개념을 탐구하여 세계가 컴퓨팅하는 방식에 혁명을 일으키고 있습니다. 무어의 법칙의 이전 장벽을 깨고 오늘날의 제품에 있는 많은 혁신은 스트레인드 실리콘, Hi-K 금속 게이트, FinFET 트랜지스터, RibbonFET 및 EMIB 및 Foveros Direct를 포함한 패키징 혁신을 포함한 구성 요소 연구의 작업으로 시작되었습니다.

우리가 하고 있는 일: IEDM 2021에서 공개된 혁신은 인텔이 3가지 경로 찾기 영역을 통해 2025년 이후에도 무어의 법칙의 발전과 이점을 계속해서 나아가고 있음을 보여줍니다.

1. 인텔은 미래 제품 제공에 더 많은 트랜지스터를 제공하기 위한 필수 확장 기술에 대한 중요한 연구를 추구하고 있습니다.

- 이 회사의 연구원들은 패키징에서 10배 이상의 상호 연결 밀도 향상을 구상하면서 하이브리드 본딩 상호 연결의 설계, 프로세스 및 조립 과제에 대한 솔루션을 설명했습니다. 상기 인텔 가속 이벤트 7 월, 인텔은 3D 스태킹의 상호 연결 밀도의 크기 증가의 순서를 제공하고, 하위 10 마이크론 범프 피치를 가능하게 Foveros 직접 소개하는 계획을 발표했다. 에코시스템이 고급 패키징의 이점을 얻을 수 있도록 인텔은 하이브리드 본딩 칩렛 에코시스템을 활성화하기 위한 새로운 산업 표준 및 테스트 절차의 수립도 요구하고 있습니다.

- 인텔은 게이트 만능 RibbonFET을 넘어, 무어의 법칙의 지속적인 발전을 위해 최대 30%~50%의 로직 스케일링 개선을 달성하는 것을 목표로 하는 다중(CMOS) 트랜지스터를 적층하는 접근 방식으로 다가오는 FinFET 이후 시대를 마스터하고 있습니다. 평방 밀리미터당 더 많은 트랜지스터를 장착함으로써

- 인텔은 또한 몇 개의 원자 두께에 불과한 새로운 재료를 사용하여 기존 실리콘 채널의 한계를 극복하고 다이 영역당 수백만 개 이상의 트랜지스터를 가능하게 하는 트랜지스터를 만드는 방법을 보여주는 미래 지향적인 연구를 통해 옹스트롬 시대로 무어의 법칙 발전을 위한 길을 닦고 있습니다. 향후 10년 동안 더욱 강력한 컴퓨팅을 위해

2. 인텔은 실리콘에 새로운 기능을 제공합니다.

- 300mm 웨이퍼에 실리콘 기반 CMOS와 GaN 기반 전원 스위치의 세계 최초 통합을 통해 보다 효율적인 전력 기술이 발전하고 있습니다. 이는 CPU에 저손실, 고속 전력 공급을 위한 단계를 설정하는 동시에 마더보드 구성 요소와 공간을 줄입니다.

- 또 다른 발전은 게임에서 AI에 이르기까지 컴퓨팅 응용 프로그램의 증가하는 복잡성을 해결하기 위해 더 많은 메모리 리소스를 제공할 수 있는 가능한 차세대 임베디드 DRAM 기술을 위한 새로운 강유전성 재료를 사용하는 Intel의 업계 최고의 저지연 읽기/쓰기 기능입니다.

3. 인텔은 실리콘 트랜지스터 기반 양자 컴퓨팅으로 엄청난 성능을 추구할 뿐만 아니라 새로운 실온 장치를 사용하여 대규모 에너지 효율적인 컴퓨팅을 위한 완전히 새로운 스위치를 추구하고 있습니다. 미래에 이러한 계시는 물리학에서 완전히 새로운 개념을 사용하여 고전적인 MOSFET 트랜지스터를 대체할 수 있습니다.

- IEDM 2021에서 Intel은 실온에서 MESO(Magnetoelectric Spin-orbit) 논리 장치의 세계 최초 실험 구현을 시연했으며, 이는 스위칭 나노스케일 자석을 기반으로 하는 새로운 유형의 트랜지스터에 대한 잠재적 제조 가능성을 보여주었습니다.

- Intel과 IMEC는 완전한 기능의 스핀-토크 장치를 실현하기 위한 장치 통합 연구를 수행하기 위해 스핀트로닉 재료 연구를 진행하고 있습니다.

- 인텔은 또한 CMOS 제조와 호환되고 향후 연구를 위한 다음 단계를 식별하는 확장 가능한 양자 컴퓨팅의 실현을 위한 전체 300mm 큐비트 프로세스 흐름을 선보였습니다.

구성 요소 연구 정보: Intel Technology Development의 연구 그룹인 구성 요소 연구는 무어의 법칙을 확장하고 Intel 제품 및 서비스를 가능하게 하는 혁신적인 프로세스 및 패키징 기술 옵션을 제공하는 책임이 있습니다. 회사의 사업부와 협력하여 미래 요구 사항을 예측하고 미국 정부 연구실 및 산업 컨소시엄에서 대학 연구 그룹 및 공급업체에 이르기까지 외부 그룹과 협력함으로써 인텔의 연구 및 개발 파이프라인을 완전하게 유지합니다.

추가 컨텍스트: 3D 적층 트랜지스터: 상향식 건물을 통한 면적 개선 (비디오) | Foveros Direct: 무어의 법칙을 이어가는 고급 패키징 기술 (비디오) | Intel의 구성 요소 연구 그룹, 혁신적인 프로세스 및 패키지 기술 발명 (비디오)

'브랜드관 > 인텔' 카테고리의 다른 글

| Mobileye, 1억 개의 EyeQ 칩 출하 기념 (1) | 2021.12.24 |

|---|---|

| 인텔, 통합 포토닉스 연구 센터 출범 (0) | 2021.12.24 |

| 메타버스에 전원 공급 (0) | 2021.12.24 |

| 인텔, AI 언어 인식 촉진 (0) | 2021.12.24 |

| 인텔, Mobileye 공개 계획 발표 (0) | 2021.12.24 |

| Inspur, Ruijie, Silicom, 인텔 IPU 생태계 확장 (0) | 2021.12.24 |

| CES 2022에서 Intel, Mobileye (0) | 2021.12.24 |

| AWS re:Invent 2021의 Intel (0) | 2021.12.24 |